Asian Journal of Information Science and Technology (AJIST) and Instumentation Engineering (IJAREEIE) Vol.2.No.1 2014 pp 1-6. available at: www.goniv.com Paper Received :08-03-2014 Paper Accepted:22-03-2013 Paper Reviewed by: 1. R. Venkatakrishnan 2. R. Marimuthu Editor : Prof. P.Muthukumar

# TESTING OF ADCS WITH DIGITAL ERROR CORRECTION BASED ON LINEARITY TEST METHOD

V.Poonguzhali , P.Meenakshi Vidya Department of Electronics and Communication Engineering Easwari Engineering College Chennai, India poonguzhali.varadarajan@gmail.com, Meenakshividya.P@gmail.com

ABSTRACT

\_\_\_\_\_

Analog to digital conversion is an important way of interpreting the real time signals into digitally understandable form, Operation of various digital media devices depends on the accurate information provided by its ADC unit like GPS operated devices, smart phones, Accelerometer etc. In existing Histogram based ADC error detection, the concept of code density is rather cost consuming which increase the linearity testing time. This work proposes an transition code error detection in a multi stages pipelined ADC circuit which greatly reduces the linearity testing time. Instead of measuring every digital code generated, the integral and differential errors can be detected by converting the digital code into linear varying transition codes using a DFT analyzing circuit. The number of pipelined stages increases the circuit complexity but greatly reduces the testing time. A transition-code based method is used to reduce the linearity testing time of pipelined analog-to-digital converters (ADCs). In addition, a simple digital Design-for-Test (DFT) circuit is proposed to help correctly detect transition codes corresponding to each pipelined stage. A novel design of Hybrid pipelining method with both coarse and fine grain architectures will be design and compared for performance excellence.

------

Index terms-Histogram based ADC, transition code, DFT (Design-for-Test)circuit.

\_\_\_\_\_

-----

#### 1. INTRODUCTION

. Analog to Digital Converters (ADCs) are widely used electronic components which often limit the performance of modern signal processing systems. Analog signals have an infinite number of output states, whereas digital outputs have a finite number of states[1]. There has been a significant effort to improve device performance, particularly for components used in wireless applications. Performance gains can be realized by at least three different methods[2].

Large gains are possible by improving device characteristics. This can be realized by using advanced processes that define today's evolving electronics manufacturing technology[3]. A second method is by improving circuit design technologies or ADC architectures. Advances and changes in circuit design may be able to provide the lacking dynamic range of current ADCs. A final method is by calibrating and compensating existing devices. Using current devices with compensation provides additional gains for existing technology. Analog signals are directly measurable quantities.Digital signals only have two states. Fordigital computer, we refer to binary states, 0 and 1.ADC compensation is especially beneficial for wide-bandwidth receivers that require a large dynamic range of operation.This chapter presents a contextual description of the problems dealt within the work: analog-digital converters (ADC)s error characterization and modeling, pipeline ADC calibration, and wireless channel estimation and modeling[4]. The problem statements and formulations are presented as follows.

A calibration and compensation scheme is known as dynamic compensation if the dynamic nature of the input signal is accounted for in the compensation procedure.These types of compensation schemes have been successful in providing increased spurious free dynamic range (SFDR) in current ADCs. Dynamic compensation requires the ADC to be calibrated in order to obtain representations of the errors involved. Information about the error functions is then used to compensate the ADC by removing the error from the ADC output samples. A variety of calibration methods have been investigated.Some examples of ADC usage are digital volt meters, cell phone, thermocouples, and digital oscilloscope.

This work will concentrate on pipeline architecture ADCs, which have become the architecture of choice for high speed and moderate to high resolution devices. These devices are particularly important in wireless receiver applications because pipeline ADCs have moderate resolution, high speed and consume low power[5]. However the dynamic range of operation is often limited in current pipeline designs. The proposal of this work is to use the intermediate stage output bits in the compensation scheme. This work focuses on defining these errors and demonstrate, that these errors can be compensated using intermediate stage outputs. This work also defines a calibration scheme unique to pipeline ADCs.

The rest of the paper is organized as follows. Section II introduces error contribution in pipelined ADCs. Section III describes the pipeline ADC architecture. Section IV shows the comparison between histogram and transition code method. Section V is based on digital error correction method with the complete test procedure in detail. Section VI explains the simulation result of phase 1. Finally, the conclusions are given in section VII.

# 2. ERROR CONTRIBUTIONS IN PIPELINE ADCS

This section addresses possible error mechanisms that can be present in a pipeline converter. Extensive work has been done on characterizing error mechanisms and an overview can be found. Pipeline Analog-to-Digital data converters have many potential error sources.Many of them are the same error source found in other ADCs. There is, however fundamental difference in how the error sources appear in the final converted signal for pipelined ADCs. The segmented nature of the Pipeline ADC is very helpful in addressing power and speed concerns, but complicates understanding and reduction of error propagation from stage to stage. Simple errors in Pipeline ADCs produce non-linearities that are difficult to correct. The following paragraphs discuss error in the offset error, gain error, non-linear error,S/H and sub-ADC.

#### A. Offset Errors:

Offset errors are simple additive errors that can be modeled as an error constant summed with the

signal. Offset errors in analog-to-digital converters are generally not difficult to compensate for especially when the offset propagates directly to the output. In such a case, a simple system-level calibration can correct this error. Common offset sources in Pipeline ADCs are charge injection, opamp offset and finite gain, comparator offset, and DAC offset.

# B. Gain Error:

Gain error is a multiplicative error that acts on the input signal. It can be modelled as a gain stage where a gain of one is the optimal gain value. Like offset error, gain error on the system level is a fairly simple error to correct. Also, just like offset error within pipelined stages, gain errors can create difficult-to-remove non-linear errors. The most common gain error sources are feedback capacitor to DAC capacitor mismatch and under-settled discretetime signals.

## C. Non-Linear Error:

Linearity is simply defined as a property of a system whereby the input-to-output characteristic is wholly linear and can be described in the form y = mx + b. There are also some error

sources in Pipeline ADCs that are inherently nonlinear. These are opamp output non-linearity, signaldependant switch resistance, and non-linear capacitance.

#### D. Sample and Hold Error:

The S/H is the first block in each stage, and determines the actual input signal bandwidth for the converter. S/H error can be modeled as a small change in the ideal input sample X. Let the held sample be represented as  $X+_X$ . The M and N-bit ADC can be used to show the effects of the sample error component \_X at various points in the pipeline architecture. Refer to figure1.

Figure 1 : An N-bit ADC connected to an M-bit ADC.

#### **3. PIPELINE ADC**

A pipeline ADC (also called subrangingquantizer) uses two or more steps of subranging. First, a coarse conversion is done. In a second step, the difference to the input signal is determined with a digital to analog converter (DAC). This difference is then converted finer, and the results are combined in a last step. This can be considered a refinement of the successive-approximation ADC wherein the feedback reference signal consists of the interim conversion of a whole range of bits (for example, four bits) rather than just the next-most-significant bit. By combining the merits of the successive approximation and flash ADCs this type is fast, has a high resolution, and only requires a small die size.

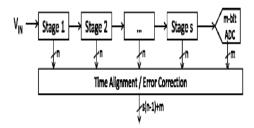

The pipelined is a popular architecture for modern applications of analog-to-digital converters due to its high sustained sampling rate, low power consumption, and linear scaling of complexity. Figure 2 shows a block diagram of a pipelined ADC. The term "pipelined" refers to the stage-by-stage processing of an input sample VIN.

In the above diagram, the analog input voltage VIN enters the ADC. Each subsequent pipeline stage of the ADC resolves a certain n number of bits to be contributed to the final conversion output. The number of bits that each stage is responsible for quantizing is usually on the order of 1 - 5 bits. Simultaneously, after each stage has finished quantizing its input sample to n bits, it outputs an analog residue voltage that serves as the input to the next stage. After s stages of conversion, an m-bit ADC resolves the lower bits of the overall ADC digital output. Each stage's digital decision is then passed to a digital block that properly timealigns the output bits and corrects for any errors in each stage. The final digital decision is then produced.The successive approximation ADC method is stated into transfer model and the transfer function are splitted into n pipelined stages.Each computations are performed as (coarse) large computation.Execution in pipelined stages and the individual pipeline stage output are grouped into digital output.

#### A. Coarse grain:

System will do large amount of computation before reporting is called as coarse grain.Major instruction sets are splitted into parallel operating instruction steps (s1,s2,s3...etc). Each steps contains sub operation like loops, dependent instruction etc.

#### Figure 3:Coarse Grain Execution Model B. FINE GRAIN:

System will do small amount of computation before transferring. The already coarse grain splitted steps are further categorized into sub steps and executed with inner fine grain architecture.

The dependent instruction cycles are adjusted to wait for the running instruction to complete.

Figure 4: Fine Grain Execution Model

Calculation involving analog to digital conversion will be stated and categorized.The categorized mathematical operation will be scheduled.The mathematical expression are sub scheduled as fine grain instruction.For example a multiplication can be converted into repeated additions.Based on the coarse grain and fine grain prediction a VLSI architecture will be developed by hybriding both pipelined architecture.

#### C. 12 Stage Pipelined ADC

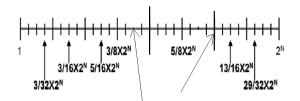

To select proper transition codes of each stage significantly determines the testing accuracyof the proposed method. In the overlapped region of Fig. 5,transition codes of the target pipelined stage are possible to be the same with those of previous stages. Under this situation, the overlapped transition codes contain nonlinearities of previousstages, and the nonlinear error effect of target stage cannotthus be correctly identified. When the overlapped transitioncodes are selected and their measured results are duplicated for other transition codes of the target stage, the nonlinear effects of previous stages are also duplicated. As a result, thetest accuracy of the proposed method is seriously degraded. To avoid this condition, the first and the last sets of transition codes of each stage, out of the overlapped region, are selected. These transition codes are impossible to be the same with thoseof previous stage when comparator offset does not exceed thetolerable value of DEC. The selected transition codes of thefirst three stages are marked with "" symbol in Fig. 5.

Fig. 5. Concept diagram for the distributions of transition codes corresponding to the first three 1.5-bit stages.

#### 4. HISTOGRAM VS TRANSITION CODES A. Histogram Method

In, a histogram is a graphical representation of the distribution of data. It is an estimate of the probability distribution of a continuous variable and was first introduced by Karl Pearson. A histogram representation is a of tabulated frequencies, shown as adjacent rectangles, erected over discrete intervals (bins), with an area equal to the frequency of the observations in the interval<sup>[7]</sup>. The height of a rectangle is also equal to the frequency density of the interval, i.e., the frequency divided by the width of the interval. The total area of the histogram is equal to the number of data.

A histogram may also be normalized displaying relative frequencies. It then shows the proportion of cases that fall into each of several categories, with the total area equaling 1. The categories are usually specified as consecutive, nonoverlapping intervals of a variable. The categories (intervals) must be adjacent, and often are chosen to be of the same size. The rectangles of a histogram are drawn so that they touch each other to indicate that the original variable is continuous. Histograms are used to plot the density of data, and often for density estimation: estimating the probability density function of the underlying variable. The total area of a histogram used for probability density is always normalized to 1. If the lengths of the intervals on the x-axis are all 1, then a histogram is identical to arelative frequency plot.

#### B. Transition code method

Transition coding is a upcoming method used to reduce the possible error occurrence in a ADC.A transition code based method is proposed to reduce the linearity testing time of pipelined ADC[8].A transition codes corresponding to each pipelined stage are shifted by comparator offsets and also at each stage are difficult to estimate.

#### C. Flow of Work:

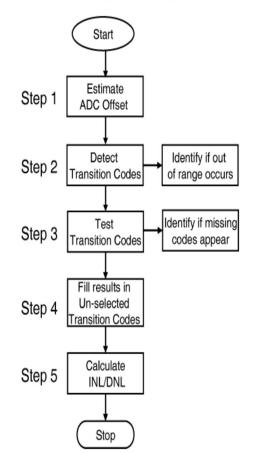

Figure 6: Test procedure of proposed transition code based method

Step 1:ADC input affects the range of input stimulus for testing transition codes of each pipelined stage. Now the ADC offset is estimated.Step 2:The immediate range exceeding digital values are detected along with the conversion of transition codes.Step 3:The detected transition codes are grouped to find the missing code occurrence of each stage.Step 4:The test result of the un-selected codes are filled with those of selected test codes.Step 5:When CBWs(code bin width) of all ADC codes are determined, the corresponding DNL and INL calculations are performed[9].

## **5. DEC TECHNIQUE**

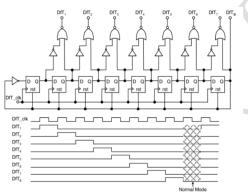

The DEC technique has been applied to relax the comparator offset requirement in pipelined ADC. In thispaper, DFTcircuit is introduced to assist in detecting transition codes of pipelined stages in ADC with DEC technique. DEC is an adjustment circuit which is capable of detecting single bit errors present during analog to digital conversion.

Figure 7: Ideal Case of Transition Edge

In this paper various pipeline stages are used for analog to digital conversion and simple paring based DEC will take place on each pipelined stage.

Figure 8: DEC Logic Diagram

# 6. SIMULATION RESULT

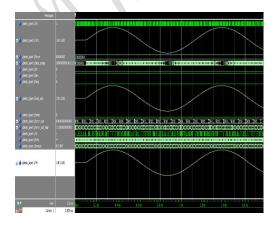

Figure 9: ADC digital error correction graph

A 32-bit pipeline stages for ADC conversion is designed and each pipeline stages output is converted into equivalent transition codes.The design of transition code based ADC digital error correction is successfully designed by using modelsim simulation tool and the result graph is shown above.

The initial analog input of volt is generated as input, the 32 level 16 bit Pipeline stages are employed for parallel analog to digital conversion. The calculated digital ADC offsets are converted into equivalent transition codes which shown in the variable xx from the above graph. The transition codes are further tested for missing and out of range codes. The sine out variable holds the differential Non linearity corrected output and the variable 'vlt' holds the integral corrected output.

# 7. CONCLUSION AND FUTURE WORK

Thus a successful recovery of the original analog signal is acquired using DFT digital error detection and correction circuitry.Coarse grain pipeline stages has the capability to convert and correct coarse analog values whereas it can't produce accurate result for fine analog values. Here fine grain pipeline stages will be combined with coarse grain pipeline stages to tune either coarse grain or fine grain analog values. The coarse grained multipipelined staged ADC can be scheduled into fine grain pipelined tuning which will further increase the accuracy and reduces the delay time with a trade of area coverage.

#### REFERENCES

[1] IEEE Standard for Terminology and Test Methods for Analog-to-Digital Converters, IEEE Std 1241-2000.

[2] H. W. Ting, B. D. Liu, and S. J. Chang, "A histogram-based testing method for estimating A/D converter performance," IEEE Trans. In strum Meas., vol. 57, no. 12, pp. 420–427, Dec. 2008.

[3] N. Andrews, "The global market for power supply and power management integrated circuits," in Seventeenth Annual IEEE Applied Power Electronics Conference and Exposition (APEC 2002). IEEE, 2002, pp. 126–131.

[4] G. N. Stenbakken and T. M. Souders, "Linear error modeling of analog and mixed-signal devices," in Proc. IEEE Int. Test Conf., Nashville, TN, Oct. 1991, pp. 573–581.

[5] Z. Yu, D. Chen, and R. Geiger, "Pipeline ADC linearity testing with dramatically reduced data capture time," in Proc. IEEE ISCAS, 1999,vol. 1, pp. 792–795.

[6] T. B. Cho and P. R. Gray, "A 10 b 20Msample/s, 35mWpipeline A/D converter," IEEE J. Solid-State Circuits, vol. 30, no. 5, pp. 166–172, Mar. 1995.

[7] M. F. Wagdy and S. S. Awad, "Determining ADC effective number of bits via histogram testing," IEEE Trans. Instrum. Meas., vol. 40, no. 8,pp. 770–772, Aug. 1991.

[8] C. Wegener and M. P. Kennedy, "Linear modelbased testing of ADC nonlinearities," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 51, no. 1, pp. 213– 217, Jan. 2004.

[9] J. F. Lin, S. J. Chang, and C. H. Huang, "Designfor-test circuit for the reduced code based linearity test method in pipelined ADCs with digital error correction technique," in Proc. IEEE Asian TestSymp, Nov. 24–27, 2009, pp. 57–62.